——Gedeelt vum DWIN Froum

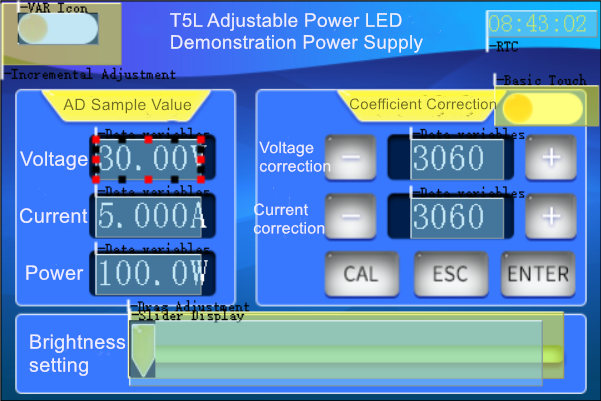

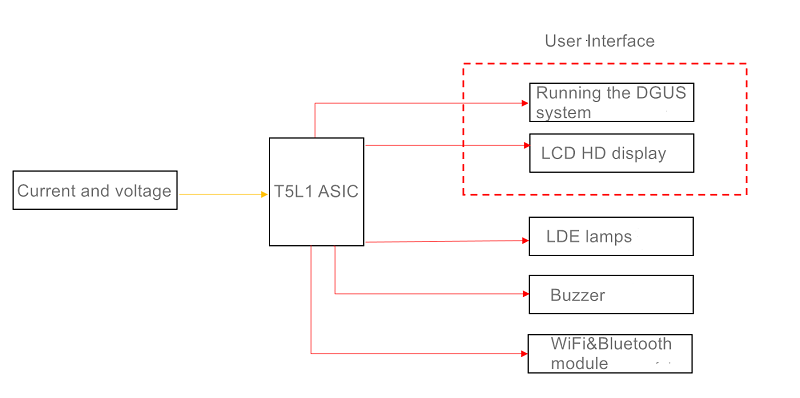

Benotzt DWIN T5L1 Chip als Kontrollkär vun der ganzer Maschinn, kritt a veraarbecht Touch, ADC Acquisitioun, PWM Kontrollinformatioun, a fiert den 3.5-Zoll LCD-Bildschierm fir den aktuelle Status an Echtzäit ze weisen.Ënnerstëtzt Fern Touch Upassung vun der LED Liichtquell Hellegkeet duerch WiFi Modul, an ënnerstëtzt Stëmmalarm.

Programm Funktiounen:

1. Adopt T5L Chip fir op héich Frequenz ze lafen, AD Analog Sampling ass stabil, an de Feeler ass kleng;

2. Ënnerstëtzung TYPE C direkt verbonne mat PC fir Debugging a Programm Brennen;

3. Ënnerstëtzung High-Speed OS Kär Interface, 16bit parallel port;UI Kär PWM Hafen, AD Port Lead Out, Low-Cost Applikatioun Design, net néideg fir zousätzlech MCU ze addéieren;

4. Ënnerstëtzung WiFi, Bluetooth Fernsteierung;

5. Ënnerstëtzung 5 ~ 12V DC breet Spannung a breet Palette Input

1.1 Schema Diagramm

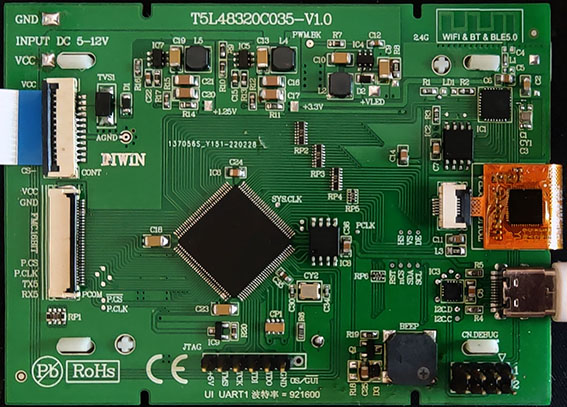

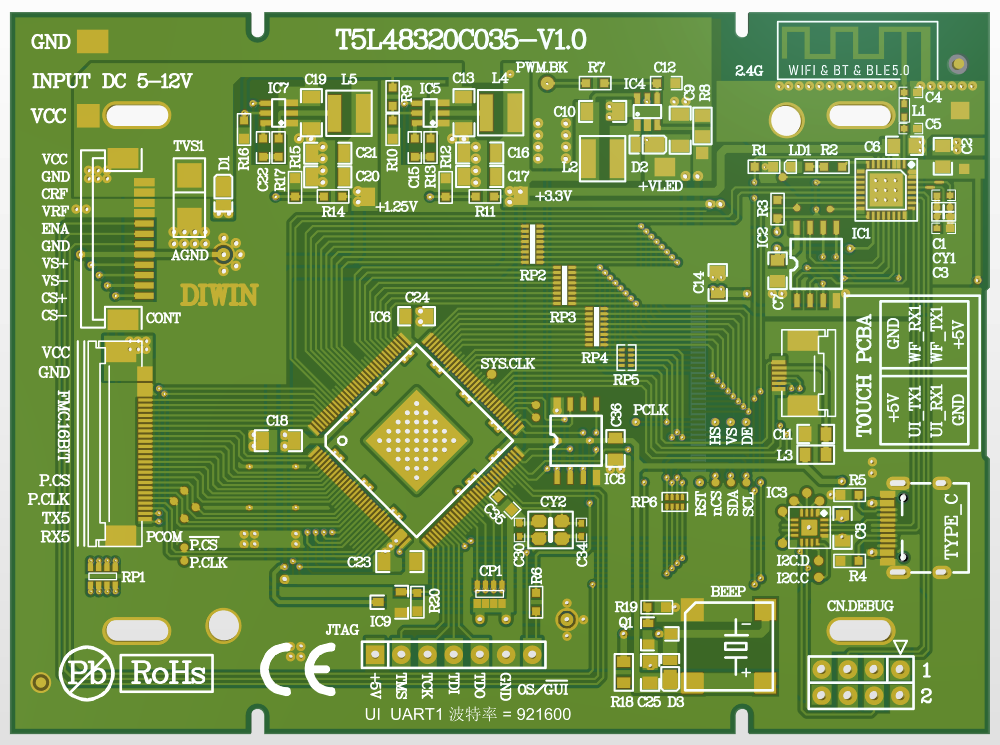

1.2 PCB Verwaltungsrot

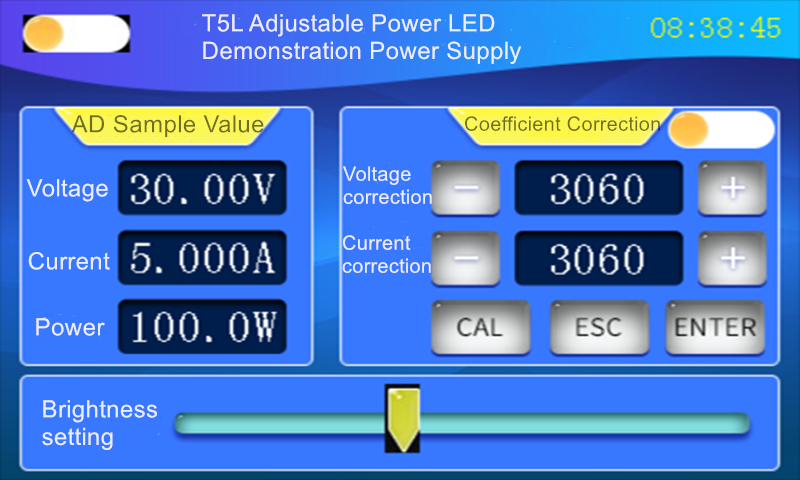

1.3 User Interface

Schimmt Aféierung:

(1) Hardware Circuit Design

1.4 T5L48320C035 Circuit Diagramm

1. MCU Logik Energieversuergung 3.3V: C18, C26, C27, C28, C29, C31, C32, C33;

2. MCU Kär Energieversuergung 1,25V: C23, C24;

3. MCU Analog Energieversuergung 3.3V: C35 ass déi Analog Energieversuergung fir MCU.Beim Typéierung kann de Kär 1.25V Buedem an de Logik Terrain kombinéiert ginn, awer den analoge Buedem muss getrennt ginn.D'analog Buedem an den digitale Buedem soll um negativ Pole vun der LDO Ausgang grouss capacitor gesammelt ginn, an der Analog positiv Pole soll och um positive Pole vun der LDO grouss capacitor gesammelt ginn, sou datt AD Sampling Kaméidi miniméiert.

4. AD Analog Signal Acquisitioun Circuit: CP1 ass den AD Analog Input Filter capacitor.Fir de Samplingsfehler ze reduzéieren, sinn den analoge Buedem an den digitale Buedem vum MCU onofhängeg getrennt.Den negativen Pol vum CP1 muss mat der minimaler Impedanz mam analoge Buedem vum MCU verbonne sinn, an déi zwee parallele Kondensatoren vum Kristalloszilléierer si mat dem analoge Buedem vum MCU verbonnen.

5. Buzzer Circuit: C25 ass de Stroumversuergungskondensator fir de Buzzer.De Buzzer ass en induktiven Apparat, an et gëtt e Peakstroum wärend der Operatioun.Fir de Peak ze reduzéieren, ass et néideg de MOS Drive Stroum vum Buzzer ze reduzéieren fir de MOS Tube an der linearer Regioun ze schaffen, an de Circuit ze designen fir et am Schaltermodus ze schaffen.Notéiert datt de R18 parallel op béide Enden vum Buzzer soll verbonne sinn fir d'Klangqualitéit vum Buzzer unzepassen an de Buzzer knusprech an agreabel ze maachen.

6. WiFi Circuit: WiFi Chip probéieren ESP32-C, mat WiFi + Bluetooth + BLE.Op der Drot sinn den RF Kraaft Buedem an de Signal Buedem getrennt.

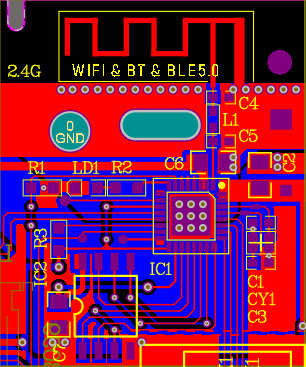

1.5 WiFi Circuit Design

An der uewe genannter Figur ass den ieweschten Deel vun der Kupferbeschichtung d'Kraaft Buedemschleife.D'WiFi Antenne Reflexioun Buedem Loop muss e grousst Gebitt zum Kraaftgrond hunn, an de Sammelpunkt vum Stroumgrond ass den negativen Pol vum C6.E reflektéierte Stroum muss tëscht dem Stroumgrond an der WiFi Antenne geliwwert ginn, sou datt et Kupferbeschichtung ënner der WiFi Antenne muss sinn.D'Längt vun der Kupferbeschichtung iwwerschreift d'Verlängerungslängt vun der WiFi-Antenne, an d'Verlängerung wäert d'Sensibilitéit vum WiFi erhéijen;Punkt op den negativen Pol vun C2.E grousst Gebitt vu Kupfer kann de Kaméidi schützen, deen duerch d'WiFi-Antennestralung verursaacht gëtt.Déi 2 Koffergrënn sinn op der ënneschter Schicht getrennt a gesammelt an d'Mëtt Pad vun ESP32-C duerch Vias.Den RF Kraaft Buedem brauch eng méi niddereg Impedanz wéi d'Signal Buedem Loop, sou datt et 6 Vias vum Kraaft Buedem op den Chip Pad sinn fir eng genuch niddereg Impedanz ze garantéieren.D'Grondschleife vum Kristalloszillator kann net RF-Kraaft duerch et fléissen, soss generéiert de Kristalloszillator Frequenzjitter, an de WiFi Frequenzoffset wäert net fäeg sinn Daten ze schécken an ze kréien.

7. Géigeliicht LED Muecht Fourniture Circuit: SOT23-6LED Chauffer Chip Sampling.D'DC / DC Stroumversuergung un d'LED bildt onofhängeg eng Loop, an den DC / DC Buedem ass mam 3.3V LOD Buedem verbonnen.Zënter datt de PWM2 Portkär spezialiséiert ass, gëtt en 600K PWM Signal eraus, an e RC gëtt bäigefüügt fir de PWM Output als ON / OFF Kontroll ze benotzen.

8. Volt Input Beräich: zwee DC / DC Schrëtt-Downloads sinn entworf.Bedenkt datt d'R13 an R17 Widderstänn am DC / DC Circuit kann net ewechgelooss ginn.Déi zwee DC / DC Chips ënnerstëtzen bis zu 18V Input, wat praktesch ass fir extern Energieversuergung.

9. USB TYPE C Debug port: TYPE C kann no vir an no hannen ugeschloss ginn.Forward Insertion kommunizéiert mam WIFI Chip ESP32-C fir de WIFI Chip ze programméieren;ëmgedréint Insertion kommunizéiert mam XR21V1410IL16 fir den T5L ze programméieren.TYPE C ënnerstëtzt 5V Energieversuergung.

10. Parallel port Kommunikatioun: T5L OS Kär huet vill fräi IO Häfen, an 16bit parallel port Kommunikatioun kann entworf ginn.Kombinéiert mat ST ARM FMC parallel port Protokoll, et ënnerstëtzt synchron liesen a schreiwen.

11. LCM RGB Héich-Vitesse Interface Design: T5L RGB Wasserstoff ass direkt un LCM RGB ugeschloss, a Prellbock Resistenz gëtt an der Mëtt bäigefüügt LCM Waasser ripple Interferenz ze reduzéieren.Wann wiring, reduzéieren d'Längt vun der RGB Interface Verbindung, virun allem de PCLK Signal, an Erhéijung der RGB Interface PCLK, HS, VS, DE Test Punkten;de SPI Hafen vum Bildschierm ass mat de P2.4 ~ P2.7 Ports vum T5L verbonnen, wat praktesch ass fir den Écran Chauffer ze designen.Féiert RST, nCS, SDA, SCI Testpunkte fir d'Entwécklung vun der Basisdaten Software ze erliichteren.

(2) DGUS Interface

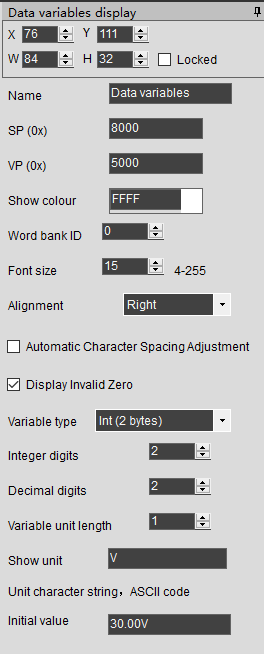

1.6 Daten Variabel Display Kontroll

(3) OS

//———————————DGUS liesen a schreiwen Format

typedef struct

{

u16 eng;//UI 16bit Variabel Adress

u8 daten;//8bitdata Längt

u8 *pBuf;//8bit Daten Zeiger

} UI_packTypeDef;//DGUS liesen a schreiwen Pakete

//——————————-Daten Variabel Display Kontroll

typedef struct

{

u16 VP;

u16 x;

u16 j;

u16 Faarf;

u8 Lib_ID;

u8 Schrëftgréisst;

u8 eng;

u8 IntNum;

u8 DecNum;

u8 Typ;

u8 LenUint;

u8 StringUinit[11];

} Number_spTypeDef;// Daten Variabel Beschreiwung Struktur

typedef struct

{

Number_spTypeDef sp;// definéieren SP Beschreiwung Pointer

UI_packTypeDef spPack;// SP Variabel DGUS liesen a schreiwen Pak definéieren

UI_packTypeDef vpPack;// definéieren vp Variabel DGUS liesen a schreiwen Pak

} Number_HandleTypeDef;// Daten Variabel Struktur

Mat der viregter Donnéeën Variabel Grëff Definitioun.Als nächst, definéiert eng Variabel fir de Spannungsprobe Display:

Number_HandleTypeDef Hsample;

u16 voltage_sample;

Als éischt, fuert d'Initialiséierungsfunktioun aus

NumberSP_Init(&Hsample,voltage_sample,0×8000);//0 × 8000 hei ass d'Beschreiwungszeechen

//——Datenvariabel déi SP Zeigerstrukturinitialiséierung weist——

void NumberSP_Init(Number_HandleTypeDef *number,u8 *value, u16 numberAddr)

{

number->spPack.addr = numberAddr;

number->spPack.datLen = sizeof(number->sp);

number->spPack.pBuf = (u8 *)&number->sp;

Read_Dgus(&number->spPack);

number->vpPack.addr = number->sp.VP;

switch(number->sp.Type) //D'Datelängt vun der vp Variabel gëtt automatesch ausgewielt no der Datevariabelentyp, déi an der DGUS Interface entworf ass.

{

Fall 0:

Fall 5:

number->vpPack.datLen = 2;

Paus;

Fall 1:

Fall 2:

Fall 3:

Fall 6:

number->vpPack.datLen = 4;

Fall 4:

number->vpPack.datLen = 8;

Paus;

}

number->vpPack.pBuf = Wäert;

}

No der Initialiséierung ass Hsample.sp d'Beschreiwungszeiger vun der Spannungssamplingdatenvariabel;Hsample.spPack ass de Kommunikatiounspointer tëscht dem OS Kär an der UI Spannungssamplingdatenvariabel duerch d'DGUS Interface Funktioun;Hsample.vpPack ass den Attribut fir d'Spannungssamplingdatenvariabel z'änneren, sou wéi Schrëftfaarwen, etc. ginn och un den UI Kär duerch d'DGUS Interface Funktioun weiderginn.Hsample.vpPack.addr ass d'Spannungssamplingdaten Variabel Adress, déi automatesch vun der Initialiséierungsfunktioun kritt gouf.Wann Dir d'Variabel Adress oder d'Variabel Datentyp an der DGUS Interface ännert, ass et net néideg d'Variabel Adress am OS Kär synchron ze aktualiséieren.Nodeems den OS Kär d'Voltage_sample Variabel berechent, brauch se nëmmen d'Write_Dgus (& Hsample.vpPack) Funktioun auszeféieren fir se ze aktualiséieren.Et ass net néideg der voltage_sample fir DGUS Transmissioun ze packen.

Post Zäit: Jun-15-2022